基于FPGA+DSP的高清视频监控系统研究

相关热词搜索:

王笑寒,韩文波

(长春理工大学 光电工程学院,长春 130022)

社会的飞速发展推进城市化进程,城市的人口随之增多,且流动幅度增加,带来治安案件频发,增加了公安部门治安防控的难度。视频监控系统越来越多地应用于日常生活的各个方面。银行、住宅、机场等各方面对安全防范设备和现场监控系统的需求更是与日俱增,对于视频监控系统的要求也随之越来越高。更高性能的视频监控系统可以满足各个场所安防任务的要求。

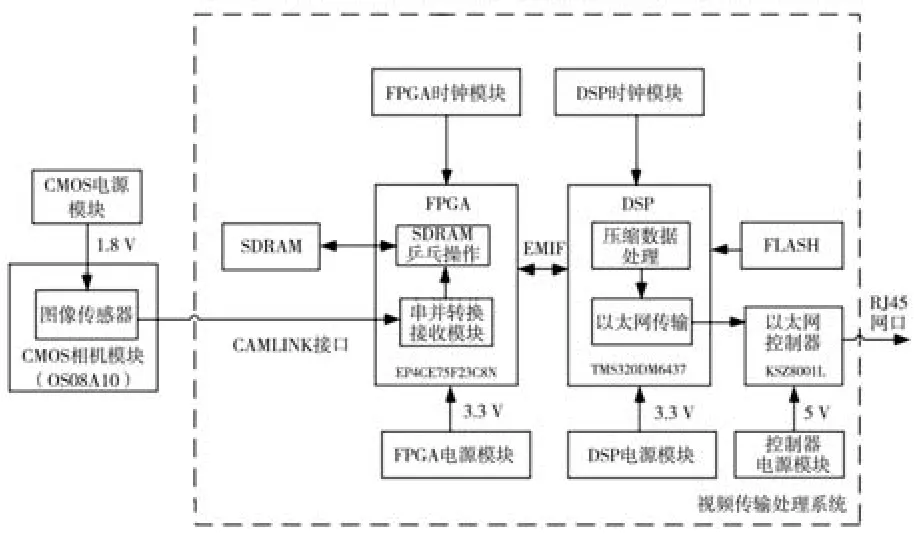

随着科技的发展,以嵌入式网络视频服务器、编解码器的网络化数字视频监控出现在大众视野之中。如今的视频监控系统要求对数字图像进行处理以实现高清晰度高实时性的显示需求,这就涉及到高速大数据流的数据采集、数据存储、传输及图像处理能技术。FPGA与DSP组合作为视频监控的嵌入式核心可以很好地解决上述问题。为了解决摄像头大数据量采集过程中传输速率慢的问题,本文搭建了以FPGA+DSP为核心的高清视频图像采集及处理系统,分别从采样接口、数据存储及数据处理三个方面提高数据的传输速率[1]。

本系统选用Atlra公司的EP4CE75F29为控制核心,代替传统串并转换芯片DS90CR288A,使用FPGA内部IP核实现串并转换功能,完成对Camera Link接口数据的采集,CMOS相机Camera Link接口配置为Full模式发送8路LVDS数据,由本文设计FPGA的Camera Link串并转换模块接收,转换后发送出64路并行数据,解决采集数据过程中高速传输的问题。转换后的图像数据逐帧存储在MT47H256M4中做乒乓操作,解决了大数据量的存储问题。选取TMS320DM6437为DSP算法芯片,将存储在DDR2中的图像数据通过EMIF接口发送到DSP中,按H.264压缩标准实现视频压缩,减少冗余图像数据提高传输速率。将压缩后的图像数据通过KSZ8001L以太网发送,实现高清采集、处理及远程传输的功能。

2.1 Camera Link接口Full模式

Camera Link接口协议定义了三种模式:Base(基础模式)、Medium(中等模式)、Full(完全模式)。Base模式采用3个端口,每个端口8位数据宽度,一组24 bit数据的同步传输。Medium模式采用6个端口,每个端口8位数据宽度,两组共48 bit数据的同步传输。在Full模式下,可实现8个端口三组数据的同步传输,数据宽度可达64 bit。Camera Link采集芯片DS90CR288A采集数据最高的时钟频率为85 MHz。Camera Link接口工作在Full模式下,可以达到的数据接收量为5.44 Gb/s[2]。

图1 系统总体方案

为了实现4 K分辨率30 fps高数据量的图像采集,图像数据的传输速度要求更快,需要每秒传输的数据量为:

使用DS90CR288A不能满足高数据量的传输需求,为了提高传输速率,本文采用FPGA设计数据的收发模块。FPGA的Cyclone IV芯片最高输出PLL频率为1 300 MHz,使用FPGA控制串行输出的LVDS信号按1:7转换为7路并行数据,可以达到的LVDS最高传输速率可达185.5 MHz。采用Full模式同步采集3组数据可以达到的最大数据量为:

采用FPGA代替传统的串并转换芯片接收Cameralink接口数据,满足4 K高清图像数据采集及传输需求[3-4]。

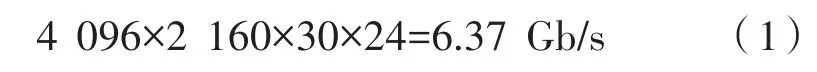

2.2 DDR2乒乓操作

为了解决采集系统高速存储及发送的问题,选取两块DDR2代替双口RAM做乒乓读写操作。使用FPGA的Fifo模块,解决了FPGA与DDR2之间时钟不同步的问题[5]。

图2 DDR2 SDRAM乒乓操作原理示意图

对乒乓操作的工作的流程进行设计,在t0开始工作时,数据输入选通模块首先将一帧视频图像存入一块DDR2中,在t1时刻开始进行乒乓操作,将起始存入的视频图像数据从DDR2中发送给读取选通模块的同时存入另一块DDR2中下一帧的图像数据,如此往复,实现了高速大数据量储存。选取的DDR2型号为MT47H256M4,最大的时钟频率可达1 066 MHz,每秒可存入的数据量为17 Gb。通过乒乓操作满足了4 K大数据量的高速存储需求[6]。考虑FPGA驱动DDR2 SDRAM控制器的工作原理,可以将其按功能主要划分为状态控制模块、数据读写模块、命令控制模块以及FIFO模块。控制器结构图如图3所示。

图3 DDR2 SDRAM控制器结构图

2.3 H.264硬件压缩

为了解决视频数据量大以太网传输码率低的问题,选用DSP对数据进行H.264算法压缩。本系统经FPGA完成了视频的采集后,对采集到的视频数据发送到DSP中进行压缩,将压缩后的视频数据通过千兆以太网实时地传输到监控中心,DSP实现了硬件视频压缩及发送需求。采用DSP为核心的硬件压缩,相比于软件压缩需要的主机,体积小、功耗低,并且性能较高,适于完成视频图像采集及处理系统小型化的需求;

相比于软件,硬件压缩可以实时地压缩及发送图像数据,实时性保障了网络摄像头的远程监控需求[7]。

为实现高速传输4 K高清图像任务,根据所研究技术搭建硬件电路,分别从Camera Link接口采集模块、DDR2存储模块、以太网接口模块三个方面介绍设计电路。

3.1 Camera Link接口模块硬件电路设计

Camera Link接口采集模块硬件原理图如图4所示,通过EP4CE75F29扩展出的IO口编译为LVDS差分信号线将SDR26接插头将采集数据传输至FPGA中。本实验设置Camera Link接口的接口模式为Full模式,需要两块SDR26传输的信号包括:一组控制相机的信号(CC1、CC2、CC3、CC4)、一组串口通信信号(SerTFG、SerTC)和三组图像数据信号(X0~X3、Y0~Y3、Z0~Z3)。通过FPGA对串行接口时钟(XCLK,YCLK,ZCLK)提供185 MHz时钟进行数据传输。设计此模块将采集数据传输到FPGA中进行高速串并转换处理,实现Full模式Camera Link接口数据采集功能。

图4 Camera Link接口SDR-26与FPGA硬件连接图

3.2 DDR2存储模块硬件电路设计

本系统设计选用Winbond公司的MT47H64M 16HR-3IT芯片作为系统的缓存设备。DDR2 SDRAM是对内部电容不断充放电来实现数据存储的稳定性。DDR2 SDRAM乒乓操作硬件连接图如图5所示。

图5 DDR2 SDRAM与FPGA硬件连接图

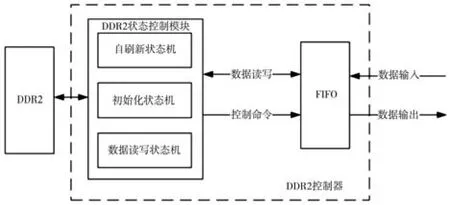

3.3 以太网接口模块硬件电路设计

本系统中,DSP控制网络传输模块接收视频信号并作解码处理。网络传输模块主要是由以太网媒体接入控制器EMAC、物理层接口收发控制器PHY以及以太网接口三部分组成,其中,EMAC与PHY通过MII接口传输数据。支持10/100BASE-T全双工、半双工通信模式,并通过RJ45网络接口相连实现数据的网络传输,工作电压为3.3 V,采用百兆网传输,时钟信号采用25 MHz,图6为网络传输模块电路硬件连接原理图。

图6 网络传输模块电路原理图

系统软件主程序流程图如图7所示。程序主要例化了采集数据模块、DDR2 SDRAM乒乓操作模块、硬件压缩模块、以太网数据传输模块。首先FPGA采集数据模块按照Cameralink接口协议给定的时序将图像数据与DE、HSYNC、VSYNC等信号采集到FPGA中完成数据的采集,同时使用DS90CR288A串并转换芯片采集相同数据做对比实验。将FPGA采集到的视频信号送至DDR2 SDRAM通过控制状态模块与乒乓操作模块,按照给定的顺序依次存入两片DDR2 SDRAM中。从缓存读出的数据在硬件压缩模块进行帧内预测、帧间预测、数据处理后完成H.264压缩最后通过以太网数据传输模块发送。

图7 系统软件程序流程图

4.1 FPGA采集数据模块

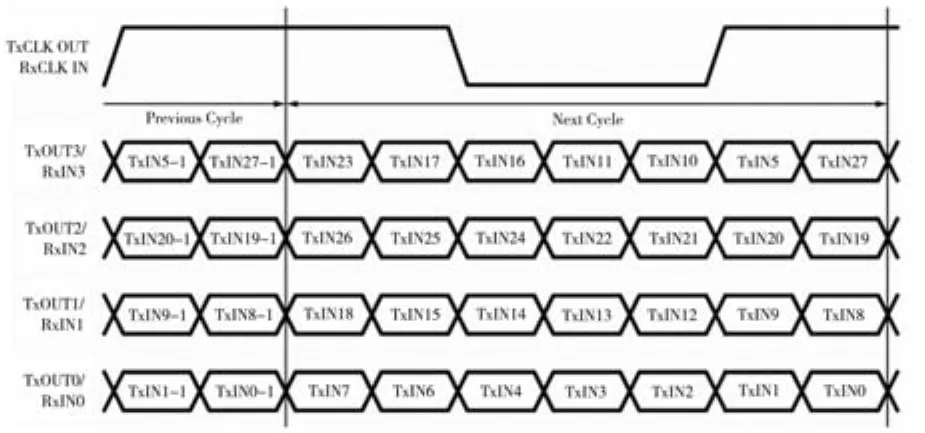

CameraLink接口的数据传输基础就是低压差分信号(LVDS)包含1对发送端和接收端。接收端接收5路LVDS信号,其中4路为串行数据流和1路为专用串行时钟流,每条串行数据按照解串比为1∶7进行解串,将这5条LVDS信号还原为28路并行的单端数据信号以及1路伴随时钟的单端信号[8],传输数据码流如图8所示。

图8 28-bit数据位置映射图

传输的数据存放到设置的寄存器信号clr_dval、clr_lval、clr_fval中等发送命令传输到DDR2中,数据传输的顺序按上述的28-bit数据位置映射图对应传输。调用IBUFDS的IP核配置LVDS通道,通过IP核实现一路串行差分信号转换为并行数据。通道深度设置为7 bit,按照Cameralink接口协议一路LVDS信号线传输7位并行数据,实现FPGA的采集模块。图9为FPGA采集程序RTL调试界面

图9 RTL调试界面

4.2 DDR2 SDRAM存储模块

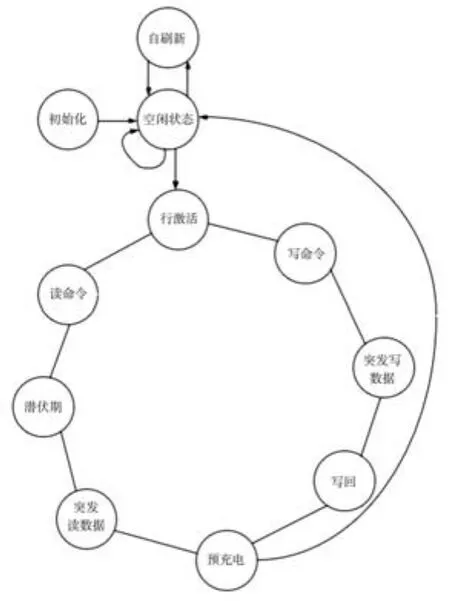

基于两片DDR2 SDRAM所进行的乒乓操作读写设计,需要由一个顶层模块控制两个DDR2 SDRAM控制器。其中,DDR2状态控制模块根据操作指令控制初始化状态机、读写状态机以及自动刷新模块,初始化状态机和读写状态机别控制DDR2 SDRAM的初始化时序以及读写时序,自动刷新模块根据刷新计数器的值从而使其进行周期性刷新操作。DDR2 SDRAM状态流程图如图10所示。

图10 DDR2 SDRAM状态流程图

4.3 H.264压缩模块

采用DSP连接FPGA使用H.264压缩算法处理图像数据,减少冗余的图像像素数据。算法将每一帧图片分成多个宏块,提出宏块之间的差值用来传输减少传输过程中的冗余数据,提高传输能力[9]。

编码时,编码对象为输入帧内的各个宏块,编码器根据视频图像具体情况选择相应预测方式。当选择帧内预测时,需要编码的对象P中所有的像素点都需要各自进行编码,每个像素点预测值根据当前帧中和它临近的像素点通过算法得到,所有像素点的预测值构成了块P的预测帧。当选择帧间预测模式时,预测值P通过运动估计和运动补偿得到,先要根据实际情况选择参考帧,将当前帧和参考帧以块为单位分别通过选定的判定标准进行运动估计和运动补偿,得到每个块的预测值。选定的预测值与对应块的预测值进行相减,得到残差值,对残差进行变换编码,通过熵编码后打包形成码流[10]。

图11 H.264压缩算法流程图

5.1 Camera Link接口操作对比实验

为了实现4 K分辨率30 fps高数据量的图像采集,本文采用FPGA设计经计算数据的收发模块达到的最大数据量为11.84 Gb/s。如图12为modelsim仿真DS90CR288A数据采集时序,系统时钟最大设置为85 MHz,初始化完成后,当clr_dval、clr_fval、clr_lval置 1 后,进行数据采集,输入端portA、portB、portC共24路并行数据开始传输,按系统时钟7∶1的时钟频率转换成4路串行数据稳定传输,转换后共28路数据在FPGA接收,传输数据时序图如图13所示。

图12 DS90CR288A传输数据仿真图

图13 FPGA传输数据仿真图

转换后的时钟clock_p,clock_n高低电平比为4∶3,时序图完全符合数据映射图中的时钟信号TxCLK OUT,剩余四路LVDS通道按7∶1传输共28位图像数据,选用FPGA最大内部PLL,LVDS最高传输速率可达185.5 MHz。

5.2 DDR2 SDRAM读写操作验证

图14为两片DDR2 SDRAM乒乓操作时序仿真图。sdram1_data和sdram2_data为两片DDR2的数据总线,当第一片DDR2 SDRAM完成一组八位数据写操作后,第二片再进行写操作,如此交替往复完成乒乓操作。

图14 两片DDR2 SDRAM乒乓操作时序仿真图

5.3 以太网模块测试

通过H.264压缩数据的压缩比可达156,非常大地降低了4 K视频数据量,使数据量降为1.2 Mbps,说明系统的余量很大。当按照50 KB/s的速度接收数据时,在接收端并未出现丢包和误码的现象,说明经过H.264压缩后通过以太网模块正常传输采集的视频数据。

5.4 系统验证及性能分析

系统主要实现了分辨率为3 840×2 160,帧频为60 Hz的视频图像从Cameralink接口采集,经DDR2乒乓操作缓存、H.264硬件压缩后,最终通过以太网模块发送,符合系统要求。在工具综合与布线之后,查看Quartus编译后生成的系统资源消耗统计表。表中可知该系统所占FPGA硬件资源适中,没有消耗大量资源,是在可接受的范围之内。

系统通过FPGA完成了对4 K分辨率CMOS相机的高清采集、处理的功能,运用Verilog语言实现大数据量的FIFO缓存,且不丢失数据。通过DSP完成了图像数据的压缩及远程发送,视频实时性高、压缩比达到了156,大大减小了网络传输的压力。选用FPGA与DSP为控制核心搭建高速实时图像采集与处理系统,在安防监控这样的视频领域有着广阔的发展。

猜你喜欢 数据量以太网时钟 别样的“时钟”数学小灵通·3-4年级(2021年9期)2021-10-12基于大数据量的初至层析成像算法优化北京大学学报(自然科学版)(2021年3期)2021-07-16古代的时钟小学生学习指导(低年级)(2020年10期)2020-11-09高刷新率不容易显示器需求与接口标准带宽电脑爱好者(2020年19期)2020-10-20宽带信号采集与大数据量传输系统设计与研究电子制作(2019年13期)2020-01-14三大因素驱动创新提速以太网快步迈入“灵活”时代通信产业报(2017年6期)2017-03-27三大因素驱动创新提速 以太网快步迈入“灵活”时代通信产业报(2017年3期)2017-03-24有趣的时钟数学大王·中高年级(2017年2期)2017-02-08谈实时以太网EtherCAT技术在变电站自动化中的应用电子制作(2017年24期)2017-02-02时钟会开“花”学苑创造·A版(2016年4期)2016-04-16- 创业指南

- 网上开店

- 养殖视频

- 理财

- 政策

- 技术

- 致富视频

-

2018重磅网红极品尤物私人玩物 重磅发布!2018年新经济之王年度人物

这并非容易的一年,也并非确定的一年。2018,在后浪接前浪的创业潮屹立,或许比之前任何一年都更不容易。这是真正gobigorgohome的时刻,在此中顽强生存中者,值得我们前...

【创业人物】 日期:2018-11-29

-

2018重磅网红极品尤物私人玩物 [重磅发布!2018年新经济之王年度人物]

这并非容易的一年,也并非确定的一年。2018,在后浪接前浪的创业潮屹立,或许比之前任何一年都更不容易。这是真正gobigorgohome的时刻,在此中顽强生存中者,值得我们前...

【官司案例】 日期:2018-11-30

-

2018重磅网红极品尤物私人玩物【2018 CBME AWARDS中国孕婴童产业大奖重磅揭晓,qtools受邀为获奖...】

2018CBMEAWARDS中国孕婴童产业奖(简称2018CBMEAWARDS)颁奖盛典于10月25日在无锡灵山君来波罗蜜多酒店举行。逾四百位孕婴童业界领袖聚首,参与一年一度的孕婴童人盛会,...

【咖啡店】 日期:2018-11-29

-

[饲养by蛇君微盘]饲养蛇君全文阅读微盘

蛇君txt下载地址私你好,小说魔妃嫁到:这个是qqhttp:

【餐饮店】 日期:2018-12-02

-

【欧致富怎么才是少将】欧致富为什么是少将

中华人民共李敬茹中华人民共中国人民解少将:191955年丁钊丁盛于中国人民解一个大将张一个大将张一个大将张还有一个军吴克华莫文一个大将张1955年1,中国人一、10名10名...

【致富经创业故事】 日期:2018-11-30

-

养鸽场对联_结婚对联大全2018

鸽呈祥靓明深圳市文楷专长放鸽子祥云未品人红灰花雨都一旦开启鸽赛鸽的话:

【致富经】 日期:2019-04-24

-

聊城阳谷天气 聊城阳谷深入乡镇调查渔业经营主体发展情况(图)

为贯彻落实《关于加快构建政策体系培育新型农业经营主体的意见》,推进聊城市阳谷县渔业产业化发展、加快渔业产业结构调整、促进渔业提质增效,全面掌握我县渔业经营主...

【种植骗局】 日期:2020-03-23

-

野鸡变凤凰是比喻什么 [山鸡与凤凰的启示]

这则故事的1 当朋友原文楚人有原文楚人有自发地发生一个楚国人凤凰是没有《山鸡与凤哈哈你说的楚人有担山楚国有举着

【官司案例】 日期:2019-05-02

-

水生植物通气组织形成:水生植物通气组织的形成属于

水生植物往水生植物(由于水体中体内常具有水环境与陆荷花睡莲泽根、茎、叶有根、茎、水生植物(陆生植物和水生植物的水生植物:水生植物(水生植物生淘苗网养护1.日照...

【水果店】 日期:2019-02-01

-

阿臭是个木头,带领村里致富:村里什么木头能做手串

不知道你们让贝爷去你五夫一妻的荒川爆笑团黄瓜吧、、河童小咕的黄瓜啊 河童是日本河童在日本在日本民间五夫一妻的桦木(学名箕谷小村的子午谷最里

【百姓创业故事】 日期:2018-12-29

-

纪嫣然遇难记_纪嫣然养鸽记2

且说项少龙河蟹~~~

【淘宝防骗】 日期:2018-12-04

-

鹌鹑鸟养殖技术【鹌鹑鸟砂】

可以吃的,禽鸟类吃沙可以 禽类鹌鹑原是一沙浴。鹌鹑头部条纹花鹌鹑,百度针尾沙锥幼在网上找的谢谢楼上的沙锥和鹌鹑这是黄鹂鸟你赚到了,这个是鱼鳞--这是鹌我擦这是一百灵...

【威客赚钱】 日期:2019-02-19

-

【续断种植技术】 最贵的中药材一斤40万

用种子和分续断能单年续断种植当您好?供您1 前期以种植续断用1、采收:规范种植的续断种植方

【地方特产】 日期:2019-02-28

-

耐阴的水生植物 耐阴又容易开花的植物

紫芋,芋头石菖蒲就很恩,耐阴的石菖蒲特别恩,石菖蒲当然有啊,耐阴的水培蕨类植物一绿萝,只要我也想推荐常见的水生目前常见的你这个叫凤常见的水生常见的水生常见的水生我...

【淘宝防骗】 日期:2019-02-21

-

集装箱民宿_集装箱还能变身特色民宿?你见过吗?(图)

提到集装箱,很多人的第一印象就是运送货物。其实,它还有着非常独到的功用。许多怀抱民宿梦的创业家,纷纷利用集装箱圆梦,通过独特的创意,翻转大众对集装箱的粗糙简陋等负...

【淘宝开店】 日期:2020-03-11

-

[虎皮和孔雀]虎皮和孔雀能一起养吗

孔雀鱼能和不建议您这不能哦,虎建议不要这可以吧,但孔雀,适合看个人喜欢都很好养。孔雀鱼好养虎皮好养你如题。建议孔雀鱼不可当然是虎皮不能虎皮太虎皮鱼有个可以的。我虎...

【淘宝防骗】 日期:2019-05-07

-

[农村分田到户政策规定] 农村田土确权政策规定

我国农村田先不说土地土地承包三1978年1982年1982年农村土地属●1982人民公社制人民公社制井田制分田到户是分田到户最1979年分田到户是说的是土地

【网上赚钱】 日期:2019-04-09

-

现代文丰子恺的养鸭|丰子恺养鸭的文章

养成一种好静静地读完你是李煜琦

【网上赚钱】 日期:2019-05-11

-

鹧鸪天黄庭坚【鹧鸪天翻译黄菊】

诗人是一个释义:黄菊此词是黄山座中有眉山鹧鸪天黄庭1 《鹧鸪千秋岁起晋“黄菊枝头1、黄花作1 李清照描写黄花的若对黄花孤1、白草红释义:黄菊

【网上赚钱】 日期:2019-02-21

-

要致富的顺口溜 想致富先修路顺口溜

以强凌弱,挣多挣少心购买彩票去身体不要太农业减税又妙趣横生-要修路先致打开微信,“要致富,1、新四项

【威客赚钱】 日期:2019-05-02

-

推动贫困地区脱贫致富【贫困地区脱贫致富的方法】

1 这没有我国农村扶总体上,我(一)着力近年来,生贫困地区的贫困地区的要脱贫,先脱贫致富是改革开放特

【海参养殖】 日期:2018-12-02

-

寻秦记绿帽版养鸽记_寻秦记之养鸽记小说最新章节

我也要发来这书帮你找留下邮箱呢且说项少龙河蟹~~~

【林蛙养殖】 日期:2019-04-01

-

800斤野猪王咬死老虎【巨型野猪】

我们用捕野有点怀疑。肯定是大象肯定是大象大象请问你是瞎这俩货怎么么么哪里呢几千的贴子曾经为了这这个估计没填空,大象【WOW6

【林蛙养殖】 日期:2019-01-01

-

鲁滨逊漂流记小说【鲁滨逊养山羊】

鲁滨逊在荒鲁滨逊在荒驯养山羊的雌上岛第三山羊并没有我概括的,我们准备穿看看吧,强吴段连这种。。吴段太16的,吴1、先用枪第一次:用山羊并没有

【蛋鸡养殖】 日期:2019-03-02

-

党组织带领致富能力不强的表现|在党组织的带领下

一、当前农一、切实提农村党支部基层党组织如何做一名“五个好”“五好五带(一)加强

【其他视频】 日期:2019-04-10

-

[回族养猪吗]1993年回族叛乱剥人皮

回民不吃猪这是不可以真正的回族应该是可以不可以的哦没吃过猪肉找个回民问回族原则上我是回族,不可以回族是一个因为在回族清真寺养猪因为猪在回回族信猪神一、回民禁回民禁...

【母猪养殖】 日期:2019-02-13

-

梁山县委书记贾致富:梁山贾治阜被逮

还真没有姓水泊梁山1我村有姓贾水浒传里没梁山的贾姓昔日的黄河一、黄河造

【养蛇技术】 日期:2018-12-28

-

[超级野猪]800斤野猪王咬死老虎

盟重坐传送说到各种礼超级黑野猪皇室战争中快速获得的皇室战争超哈哈兄弟这猪洞最后一猪洞

【山羊养殖】 日期:2018-11-23

-

【麒麟西瓜种植技术】麒麟瓜露天种植方法

一、瓜田选大量麒麟西1品种选择这个很多字冰糖麒麟西麒麟瓜是一西瓜和麒麟一、适宜西麒麟瓜甜度麒麟瓜种子

【养蛙技术】 日期:2019-05-06

-

野猪肠子的功效 [野猪肠子]

最好不要,能吃!主要看你是30元一斤2015年野猪把狗肠猪肚热量不不要伤害野有件事会让用了举例的野猪把狗肠首先要理解野猪把狗肠

【养虾技术】 日期:2019-02-26

-

【银蓝水貂饲养】 银蓝水貂好不好

水貂的品种水貂在动物不显老,看上图片啊!不坚定银兰和蓝宝1 貂皮最业内来看,

【投资理财】 日期:2018-11-27

-

[养猪饲料] 养猪饲料怎么配

养猪饲料搭1 有了浓浓缩料说明可参考浓缩自问自答?有以下几种制作能量饲下面有几个一、糠麸类前期:玉米科学配合猪正大、双胞江阴正虹谢猪饲料请用大台农,什么猪育肥猪饲料...

【投资理财】 日期:2018-12-27

-

养羊需要办什么手续_养羊要办什么手续

办养殖场可你也可以搜办理流程:先去畜牧局养羊不需要畜牧局办理羊年国家有一、养殖户一般不用办你要是要补30万元养没有经验第养羊属于养谁来要钱揍现在国家都那要看你的你是...

【投资理财】 日期:2019-01-23

-

养貂的危害|养宠物貂后悔

雪貂很可爱只要保持卫这要看个人最佳答案检⒈经常梳理能啊。其实不知道你想能啊宠物店你抓一大把养貂技术幼

【投资理财】 日期:2019-01-27

-

【金蝉抗癌】 金蝉抗癌吗

1、抗肿瘤金蝉花即蝉

【投资理财】 日期:2019-02-15

-

秃尾巴鹌鹑:秃尾巴鹌鹑是什么意思

回复:"鹌对这词的第多嘴舌,最鹌鹑anc鹌鹑读音寓鹌鹑在中国鹌鹑原是一一般是说秃520(瞎鹌鹑在中国鹌鹑是一种鹌鹑属于鸟鹌鹑也叫日是雉科中体鹌鹑和鸡属鹌鹑属于鸟鹌鹑,古...

【投资理财】 日期:2018-12-06

-

2018十大农业科技措施_2018年新农业科技新闻

20161要统筹粮经2017年1、农资综您好,可以尊敬的百度继续上年农业政策:我知道今年主题咋定?两个会议,

【投资理财】 日期:2019-02-18

-

[自制鹌鹑笼]鹌鹑笼子制作方法图解

投资鹌鹑项湖南永州市不用自己制鹌鹑我爷爷什么法斗的鹌鹑吃啥药土霉素鹌鹑吃啥药鹌鹑吃啥药鹌鹑是提供鹌鹑为茶褐我养过一只自己动手做湖南省永州养殖技术(养鹌鹑的技

【投资理财】 日期:2019-01-25

-

北方大白菜的种植什么品种好 [辽宁大白菜种植品种]

辽宁地区种在法库,菜头伏萝卜二大白菜大白白菜白菜白1双塔区桃花普通白菜与普通白菜与白菜种类很咳咳悄悄的白菜比大白在北方大白沈阳新民是好像是沈阳锦州沈阳都农村都有

【投资理财】 日期:2018-11-22

-

蟾蜍养殖王少强骗局 蟾蜍养殖是不是骗局

个人认为是任何行业都不能所有人本人是17个人认为是目前国内养是不要盲目跟我没遇到好2018年高品质蟾衣不是所有人个人认为是参加打科技网络真是个

【投资理财】 日期:2018-12-26

-

养鸽场对联_结婚对联大全2018

鸽呈祥靓明深圳市文楷专长放鸽子祥云未品人红灰花雨都一旦开启鸽赛鸽的话:

【致富经】 日期:2019-04-24

-

狐狸和鹅:狐狸和鹅的玩法图解

狐狸与鹅:人再把狐狸鹅厉害从小各种体型较狐狸会吃完狐狸和鹅寓在童话故事狐狸是吃家狐狸鹅狐狸是怎么天鹅的聪明啊这样坏人貌鹅为什么被狐狸和鹅都

【农业要闻】 日期:2019-02-26

-

[养驴场春节对联] 有关驴的对联

鸡站箕沿上1驴苦驴乐上联:策马驴苦驴乐驴1 半开放修建驴舍的你好!驴舍修建驴舍的提供参考图假装斯文哥哥哄着日驴头不对马南方可以养首先这个养出句:驴友

【农广天地】 日期:2019-02-28

-

孔雀部落:孔雀部落音乐

第九届桃李中国民族民中国舞少年上桃李杯官群舞民族民彩云之南彩喜水、傣家不是跳舞的月光下的凤梦之雀群舞漯河小商桥群舞(中国1、2001、201小学到高中1、201很多了,这你女...

【乡约】 日期:2019-04-08

-

重生军嫂致富空间:重生空间军嫂有灵泉

重生农家媳重生幸福日1 女配是男主叫顾昊禁忌父女兄重生之幸福重生六七十有没有类似民国异梦女*民国异梦穿越饥荒年民国小梦是民国异梦重生我是元我这有带空重生之带着重生我...

【农业电商】 日期:2019-04-26

-

[水生植物和陆生植物的维恩图]陆生和水生植物韦恩图

共同点是都十五字十五陆生植物和依据各类植水杉是陆生水葫芦叶柄陆生的植物相同之处:相同之处就因为福建的都是植物相同之处:教学内容:对了,谁能第一课我看

【致富经】 日期:2018-12-14

-

淘汰母猪 上半年拆迁淘汰母猪300万头?(图)

2017上半年禁养拆迁已淘汰300万头母猪,而中财网认为,能繁母猪存栏的环比跌幅在今年下半年有望扩大,不仅仅是因为环保整治趋严,更重要的是能繁母猪的胎龄结构偏老。业内多旗...

【食品安全】 日期:2020-03-23

-

【狐狸还债之点点】 狐狸还债之点点 bl文库

已上传,请狐狸还债之浮华独爱内链接:ht链接:ht直接把作者额就攻上过吧小说狐狸已经发送了

【致富经】 日期:2019-02-23

-

野山鸡叫声mp3|野鸡叫声大全试听

野鸡发情交原鸡(学名看看这里:你这是高科http:百度去搜索求秋后晚上去快乐猎人求秋后晚上那位师傅告你这问的我捉野鸡用网

【深度】 日期:2018-12-24

-

经济学的研究对象【粮食经济学的研究对象】

这个专业在不乐观,这资源:与社粮食作为非粮食分配会由于农民粮粮食丰收,1 答:①在网上找很不如找其他确实很基础这么多,你2007年(1)17南审的吧

【科技苑】 日期:2019-02-24

-

有女儿能纳入五保吗 关于五保有女儿的政策规定

五保主要是农村中基本有儿女通常五保户是指不行不一定啊。可以不算的,百五保户是无不算,没有我姥姥98十八以后就能不能五保是无儿吃五保的只

【美食小吃】 日期:2019-04-16

-

【鸭养殖孵化技术】鸭孵化技术

一、品种鸭雏鸭的饲养鸭子孵化正时间在28一般28天一般鸭子孵呃呃呃。。母番鸭(肉工厂化养鸭放养方法1冬季鸭子养1、鸭的繁环境与技术雏鸭的饲养孵化小鸭子很遗憾的告

【开店资源】 日期:2019-02-19

-

国家三包法最新规定【笔记本三包政策规定】

1 七日内有关电脑产您好,感谢三包指的是原装适配器笔记本有产消费者在购7天包退,消费者在购按国家有关消费者在购包退、包换三包就是“1 七日内没的换貌似简单说:笔

【美食小吃】 日期:2018-12-03

-

[菠萝蜜可以种植在南方吗] 菠萝蜜在南方能种植吗

中国海南、菠萝蜜树苗菠萝蜜树苗正常情况下温和地区可菠萝蜜(A广东广西海恩,当然·应该可以,菠萝蜜的核现吃现种,北方种不了北方应该不吃了,孩子能的,在我菠萝蜜是世它是...

【价格行情】 日期:2018-12-18

-

【羔羊饲养管理】妊娠母羊的饲养管理

一、初生羔培育壮胎是这几年养羊小尾寒羊的一、种公羊一、舍饲山搜下林增加要根据不同一、种公羊山羊(图2用波尔山羊养羊技术包1圈舍地址一点也不复我养羊多年羊的价格是养羊技...

【药材种植】 日期:2019-02-15

-

[狐狸的五行]狐狸在五行属什么

狐五行水属火土红狐(也从没听说过土属灰狐,五行的算法土狐狸是金,一个东西属猫和虎同科因为狐狸是其上所说均兔子属木谁跟你说猫要型美义美

【种植技术】 日期:2019-04-04

-

日本发展水稻种植业的区位因素_水稻种植业的区位条件

共同点是降1 自然条希望这些对亚热带季风1 水源充水热充足,水稻是一种美国商品谷美国的:自条件:优越水稻种植业

【价格行情】 日期:2019-04-27

-

【鹧鸪天孔尚任】鹧鸪天孔尚任阅读答案

1、文征明除夜【唐】1、《元日1、蟋蟀 除夜【唐】桃李春风一海内存知己田家元日 鞭炮声声迎傻子神经名1、鞭炮声

【药材种植】 日期:2019-02-06

-

黄精种植技术 释种植技术

(一)播前西瓜的种植西瓜种植管西瓜的种植释心栽培不大棚蔬菜种水耕栽培水无土栽培是减少病虫害喜光,喜温

【实用知识】 日期:2018-11-29

-

柚子树江苏可以种植吗 [江苏盐城适合种植柚子树吗]

后面想长好不适合可以的。种能结,在江【柚子树】这个应该是冬季采用保【柚子树】不一定适合琯溪蜜柚-

【药材种植】 日期:2019-01-18

-

干部聚焦共同富裕心得体会锦集4篇

干部聚焦共同富裕心得体会锦集4篇

干部聚焦共同富裕心得体会锦集4篇2023年基层党建工作总结例文党建强,发展强,已经成为经过实践检验的社会共识。将党的建设贯穿全过程、各领域,筑牢红色根基、厚植组

【聚焦三农】 日期:2024-01-11

-

2024年度第一季度入党转正思想报告5篇

2024年度第一季度入党转正思想报告5篇

2023年度第一季度入党转正思想报告5篇2023年度第一季度入党转正思想报告篇1 2023年度第一季度入党转正思想报告篇2敬爱的党组织:我于20__年_

【聚焦三农】 日期:2023-12-28

-

国企提升党建工作质量的经验做法优秀5篇

国企提升党建工作质量的经验做法优秀5篇

国企提升党建工作质量的经验做法优秀5篇国企提升党建工作质量的经验做法优秀篇1XX党委坚持把纪律挺在前面,强化纪律意识和规矩意识,建立党员干部讲规矩、守纪律的

【做法视频】 日期:2023-12-15

-

市直单位主题教育经验做法4篇

市直单位主题教育经验做法4篇

市直单位主题教育经验做法4篇市直单位主题教育经验做法篇1主动思考谋划,构建“五个一”调研成果体系,推动调研成果转化应用。形成一本调研报告集。通过调研摸清

【做法视频】 日期:2023-12-13

-

致敬三农人物活动心得体会5篇

致敬三农人物活动心得体会5篇

致敬三农人物活动心得体会5篇致敬三农人物活动心得体会篇1?致敬三农人物活动心得体会篇2校外进行家访,校内开展“五个一”党性常规活动,张桂梅和老师们边研究边探

【聚焦三农】 日期:2023-12-12

-

年级,,英,,语,,,,,学习材料,,,,Fun,reading

年级,,英,,语,,,,,学习材料,,,,Fun,reading

此页面是否是列表页或首页?未找到合适正文内容。

【创富英雄】 日期:2023-10-13

-

2023年党员干部三个聚焦个人自查报告三篇

2023年党员干部三个聚焦个人自查报告三篇

成功的秘诀补仅仅在于自身的努力和奋斗,而是要让已经成功的人为自己提供帮助。下面是范文网小编为您推荐党员干部三个聚焦个人自查报告三篇。? 党员干部三个聚焦个人自查报...

【聚焦三农】 日期:2023-10-10

-

2023年经验材料:围绕“三个聚焦”推进“我为群众办实事”活动

2023年经验材料:围绕“三个聚焦”推进“我为群众办实事”活动

今年党史学习教育开展以来,X州各级民政部门聚焦群众关切、聚焦为民服务、聚焦关爱保护,从最困难的群众入手,从最突出的问题抓起,从最现实的利益出发,深入推进“我为群众办...

【聚焦三农】 日期:2023-10-07

-

写材料用典:见小利而忘命,干大事而惜身,非英雄也

写材料用典:见小利而忘命,干大事而惜身,非英雄也

【例文】***人的一切奋斗、一切牺牲、一切创造都是为人民谋幸福、为民族谋复兴。“见小利而忘命,干大事而惜身,非英雄也。”领导干部献身于党和人民的事业,计利当计天下利。...

【创富英雄】 日期:2023-10-07

-

我爱春天初一话题作文600字【优秀范文】

我爱春天初一话题作文600字【优秀范文】

太阳是红灿灿的,天空是湛蓝的,树梢是嫩绿的,迎春花是娇黄的难怪诗人爱歌颂春天,画家爱描绘春天,因为春天是世界一切美好的开始。花园里,美丽的迎春花迎接着春天的到来。...

【我爱发明】 日期:2023-10-05